CBCS SCHEME CENTRAL LIBRAR 17CS72 USN Seventh Semester B.E. Degree Examination, Feb./Mar. 2022 **Advanced Computer Architectures** Time: 3 hrs. Max. Marks: 100 Note: Answer any FIVE full questions, choosing ONE full question from each module. Module-1 Discuss the elements of modern computer systems with diagram. 1 a. (10 Marks) Consider the execution of an object code with 2,00,000 instructions on a 400 MHz b. processor. The program consists of four major types of instructions. The instruction mix and the number of cycles (CPI) needed for each instruction type are given below based on the result of a program trace experiment : Instruction Mix Instruction Type CPI Arithmetic and Logic 60 % 1 2 18 % Load / Store 12 % Branch 4 Memory reference 8 10 % Calculate the average CPI when the program is executed on a uniprocessor with the i) above trace results. Calculate the corresponding MIPS rate based on the CPI obtained in part (i). (10 Marks) ii) OR Explain the different types of shared memory processors with diagram. 2 (10 Marks) a. Discuss the various static interconnection networks with bisection width, node degree, b. diameter and number of links. (10 Marks) Module-2 Compare the characteristics of CISC & RISC architectures, with the aid diagram. (10 Marks) 3 a. Explain the architectures of a VLIW (Very Long Instruction Word) processor and its b. pipeline operations. (10 Marks) OR. Draw the architecture of SPARC processor and floating point unit on two separate chips. 4 (10 Marks) b. Explain the memory page replacement policies used in Virtual Memory Technology. (10 Marks) Module-3 Explain the Fully – associative cache organisation with mapping examples. 5 a. (10 Marks) b. Design a pipeline unit for fixed point multiplication of 8 – bit integers using CSA and CPA. (Carry Save Adder and Carry Propagation Adder). (10 Marks) OR

Any revealing of identification, appeal to evaluator and /or equations written eg. 42+8 = 50, will be treated as malpractice.

Important Note : 1. On completing your answers, compulsorily draw diagonal cross lines on the remaining blank pages.

1 of 2

**6** a. Discuss the central and distributed arbitration techniques with the aid of timing diagrams.

(10 Marks)

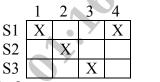

b. Consider the following pipeline reservation table :

- i) What are the Forbidden latencies?

- ii) Draw the state transition diagram.

- iii) List all the sample and greedy cycles.

- iv) Determine the optimal constant latency cycle and minimum average latency.

- v) Determine the throughput of the pipeline, if the pipeline clock period be  $\tau = 20$  ns.

(10 Marks)

(10 Marks)

(10 Marks)

## Module-4

- 7 a. Explain the cache coherence problems in data sharing and in process migration with possible solution. (10 Marks)

- b. Describe the architecture of the connection machine cm 2 with processor array and processor nodes. (10 Marks)

## OR

8 a. Compare the static and dynamic data flow computers. Draw the dataflow graph for computing cos x.

$$\cos x \approx 1 - \frac{x^2}{2!} + \frac{x^4}{4!} - \frac{x^6}{6!}$$

b. Explain the three types of cache directory protocols.

## Module-5

9 a. Explain the Shared – Variable model of parallel models.(10 Marks)b. Describe the principles of Synchronization.(10 Marks)

## OR